# 40 MHZ ACQUISITION CARD CHARACTERIZATION

Thursday, April 05, 2001

| 40 MHZ ACQUISITION CARD CHARACTERIZATION             |   |  |

|------------------------------------------------------|---|--|

| 1. VIDEO TO PIXEL CLOCK DELAY                        | 3 |  |

| 1.1. ALL BNC<br>1.2. Fanout card (All Backplane)     | 3 |  |

| 2. MEASURE STROBE RANGE                              | 4 |  |

| 3. CLOCKS SETUP                                      | 4 |  |

| 3.1. FRAME   3.2. LINE   3.3. TIMING CHARACTERISTICS | 5 |  |

# 1. Video to Pixel Clock delay

### 1.1.All BNC

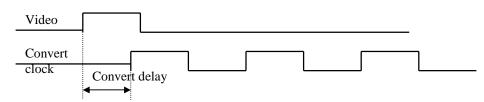

When the pixel clock is supplied on the front BNC connectors of the acquisition card, there is a delay between the Video input and the convert clock, with the convert clock delayed. This delay varies between approx 42 ns (when the Pixel Clock period is 25 ns), and 476 ns (when the Pixel Clock period is  $4 \mu s$ ).

The following table is an empirical determination of this delay at various frequencies.

|            |          | Video -> Convert | Measure Strobe | Measure Strobe      |  |

|------------|----------|------------------|----------------|---------------------|--|

| Freq [MHz] | Per [ns] | delay [ns]       | Range [ns]     | Range [% of Pxlclk] |  |

| 40.000     | 25       | 42               | 26.8           | 107.20%             |  |

| 33.333     | 30       | 41.5             | 30             | 100.00%             |  |

| 28.571     | 35       | 41.1             | 35             | 100.00%             |  |

| 25.000     | 40       | 41.2             | 40             | 100.00%             |  |

| 22.222     | 45       | 41               | 45             | 100.00%             |  |

| 20.000     | 50       | 41               | 50             | 100.00%             |  |

| 16.667     | 60       | 41               | 59.6           | 99.33%              |  |

| 14.286     | 70       | 40.7             | 72.4           | 103.43%             |  |

| 12.500     | 80       | 41               | 82.2           | 102.75%             |  |

| 11.111     | 90       | 40.8             | 92.5           | 102.78%             |  |

| 10.000     | 100      | 41               | 103.8          | 103.80%             |  |

| 9.901      | 101      | 100              | 68             | 67.33%              |  |

| 9.091      | 110      | 101              | 76             | 69.09%              |  |

| 8.333      | 120      | 102              | 85             | 70.83%              |  |

| 5.000      | 200      | 110              | 152            | 76.00%              |  |

| 3.333      | 300      | 120              | 236            | 78.67%              |  |

| 2.500      | 400      | 130              | 326            | 81.50%              |  |

| 2.000      | 500      | 142              | 414            | 82.80%              |  |

| 1.000      | 1000     | 194              | 840            | 84.00%              |  |

| 0.800      | 1250     | 220              | 1056           | 84.48%              |  |

| 0.667      | 1500     | 244              | 1276           | 85.07%              |  |

| 0.571      | 1750     | 269              | 1488           | 85.03%              |  |

| 0.500      | 2000     | 290              | 1710           | 85.50%              |  |

| 0.400      | 2500     | 340              |                |                     |  |

| 0.333      | 3000     | 386              |                |                     |  |

| 0.250      | 4000     | 476              |                |                     |  |

At frequencies between 10 MHz and 40 MHz the delay is pretty much constant : 41ns, and a fixed delay line (a coax cable) will be enough to compensate for it. At frequencies below 10 MHz, we recommend using a variable delay line.

The user is adviced to use the AD CONV CLOCK and VIDEO MONITOR outputs to adjust the timing. We recommend using a coaxial cable to generate an extra delay for the video input, so that it alligns with the convert clock.

FAILURE TO ALIGN THE VIDEO INPUT WITH THE CONVERT CLOCK, WILL RESULT IN ERRORS IN THE ACQUISITION PROCESS: PIXELS WILL BE SKIPPED AND THE "MEASURING STROBE" ADJUSTMENT WILL NOT WORK PROPERLY.

#### 1.2. Fanout card (All Backplane)

When the fanout card is used to drive the clocks (Pixel, Line and Frame) an extra delay of 52 ns is introduced. The user should compensate for this delay again, by monitoring the AD CONV CLOCK and VIDEO MONITOR outputs to adjust the timing.

### 2. Measure Strobe range

The range over which the Measure Strobe varies is shown in the above table.

At frequencies between 10 MHz and 40 MHz the range delay is pretty much constant: 100%. At frequencies below 10 MHz, the range varies between 75% and 85%.

## 3. Clocks setup

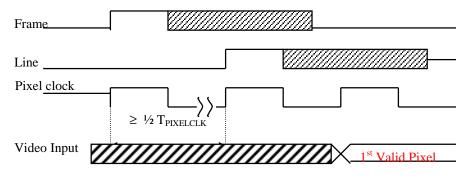

The Frame and Line clocks are sampled by the Pixel clock on the rising edge.

First the Frame clock is sampled: the detection of a Frame pulse arms the acquisition card.

Then the Line clock is sampled, and a valid Line pulse triggers the acquisition.

The first valid pixel is the pixel following the first rising edge of the Line clock, following the detection of a Frame clock pulse.

The LINE CLOCK must NOT be sampled on the same PIXEL CLOCK as the FRAME. There must be a DELAY of at least HALF of a PIXEL CLOCK between FRAME and LINE.

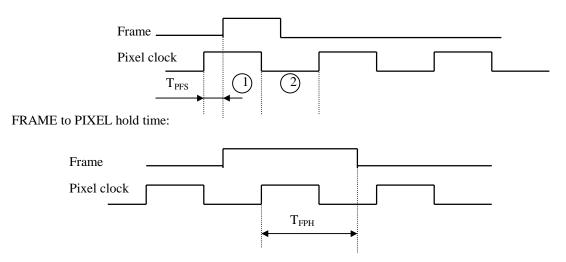

#### 3.1. Frame

The FRAME CLOCK has to meet the following time requirements with respect to the PIXEL CLOCK. All measurements were taken at the BNC front panel connectors.

PIXEL to FRAME setup time:

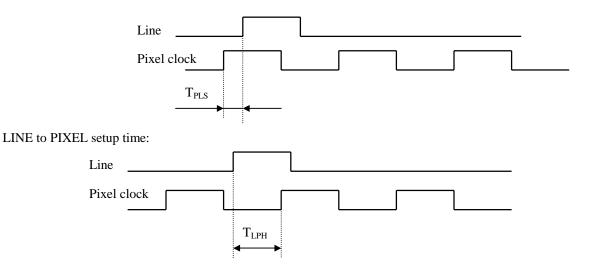

#### 3.2. Line

The LINE CLOCK has to meet the following time requirements with respect to the PIXEL CLOCK. All measurements were taken at the BNC front panel connectors.

LINE to PIXEL setup time:

## 3.3. Timing Characteristics

The following table describes the setup times for the Frame and Line "Pulses":

| Parameter        | Description            | Min [ns]                                          | Max [ns] | Notes |

|------------------|------------------------|---------------------------------------------------|----------|-------|

| T <sub>PFS</sub> | Pixel to Frame Setup   |                                                   | 0.2      | (1)   |

| T <sub>FPH</sub> | Frame after Pixel Hold | <sup>1</sup> / <sub>2</sub> T <sub>PIXELCLK</sub> | -        |       |

| T <sub>PLS</sub> | Pixel to Line Setup    |                                                   | 3        | (1)   |

| T <sub>LPH</sub> | Line after Pixel Hold  | <sup>1</sup> / <sub>2</sub> T <sub>PIXELCLK</sub> | -        |       |

Notes:

If the Pixel Clock Precedes this "Pulse" by more than the Max specified value, the "Pulse" will be sampled on the next Pixel Clock.